8085 Microprocessor Architecture

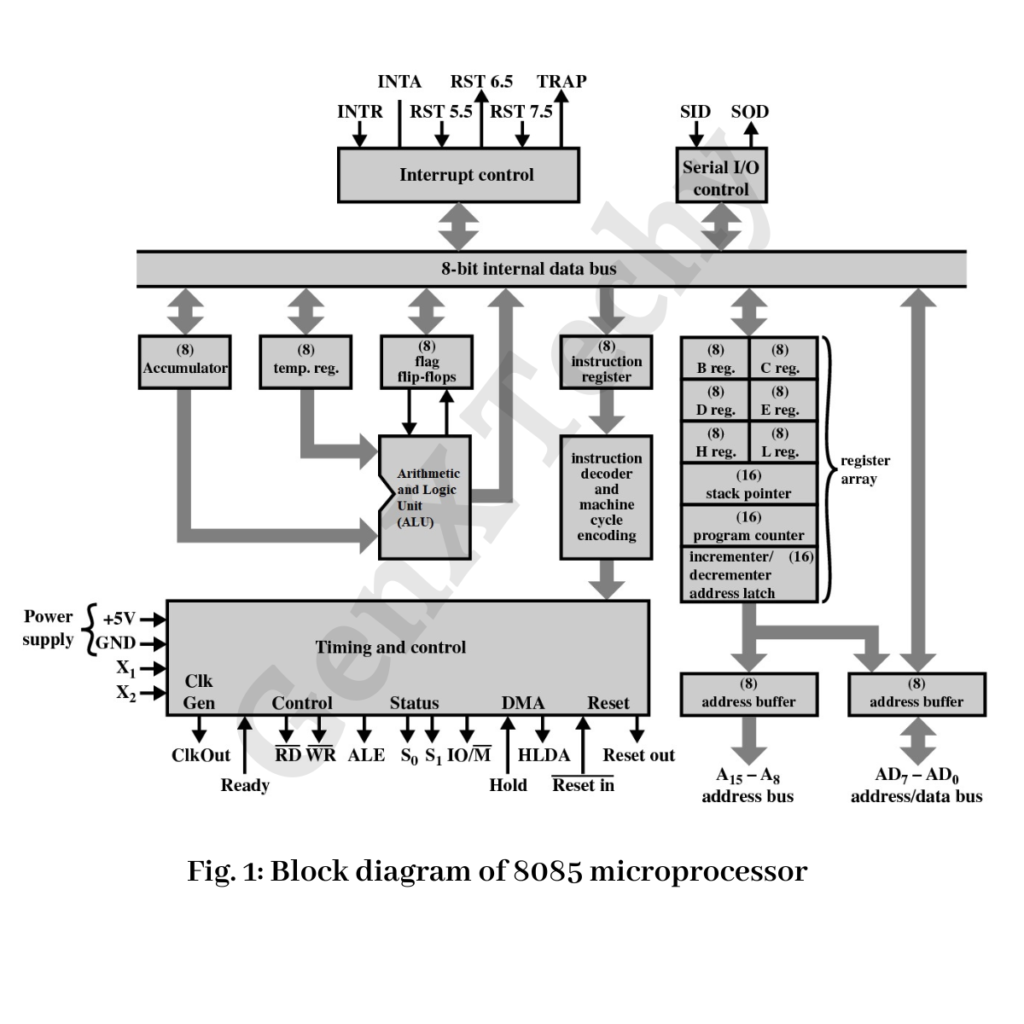

The 8085 is called an 8-bit processor since its data length and data bus width is 8-bits. It has an addressing capability of 16 bits, that is, it can address 216 = 64 KB of memory (1 KB = 1024 bytes). 8085 microprocessors generally available in 40 pin IC package and uses +5V as power supply. It can run at a maximum frequency of 3 MHz. Fig. 1 shows the block diagram of 8085 microprocessor. The processor contains Seven (7) functional units:

- Arithmetic and Logic Unit

- General Purpose Registers

- Special Purpose Registers

- Instruction Register and Decoder

- Timing and Control Unit

- Serial I/O Control Unit

- Interrupt Control Unit

1. Arithmetic and Logic Unit

Arithmetic and Logic Unit (ALU) is the circuitry that performs the arithmetic (Addition, Subtraction, Increment and Decrement, etc) and Logical (AND, OR and XOR, etc) operations. It is the fundamental component of a central processing unit (CPU) of microprocessor responsible for performing arithmetic and logical operations on data.

a) Arithmetic Operations:

- Addition: One of the most fundamental arithmetic operations, addition involves taking two numbers (operands) and producing their sum. The ALU adds binary numbers bit by bit, taking carry-in from the previous bit and generating a carry-out for the next bit. The result is stored in a destination register.

- Subtraction: Subtraction is performed similarly to addition, with borrow-in and borrow-out bits. The ALU subtracts the second operand from the first and stores the result.

b) Logical Operations:

- AND: The ALU performs a bitwise AND operation between corresponding bits of two operands. If both bits are 1, the result is 1; otherwise, it’s 0.

- OR: It performs a bitwise OR operation between corresponding bits of two operands. If at least one bit is 1, the result is 1; otherwise, it’s 0.

- XOR (Exclusive OR): XOR returns 1 if the bits being compared are different; otherwise, it returns 0. It’s often used for tasks like toggling bits.

- NOT (Complement): This operation inverts the bits of a single operand, turning 1s into 0s and vice versa.

c) Rotate Operations:

- Rotate Left (RLC): RLC rotates the bits to the left, carrying the leftmost bit to the rightmost bit and into the carry flag.

- Rotate Right (RRC): RRC rotates the bits to the right, carrying the rightmost bit to the leftmost bit and into the carry flag.

d) Comparison Operations:

- Compare (CMP): This operation subtracts two values without storing the result, setting flags in the flag register to indicate the relationship between the values (e.g., greater than, less than, or equal).

2. General Purpose Registers

- A register is a collection of 8 D-type flip-flops with parallel-in and parallel-out operations. A flip-flop can only store one bit at a time. Therefore, to handle 8-bit at a time, 8 flip-flops are required and hence the term 8-bit register.

- Though the registers are all storage areas inside the microprocessor, they differ in the purpose of storage. The general-purpose registers are used to store only the data that is being used by the program under execution and the results obtained from it. These general-purpose registers are user accessible by through programs.

- As shown in Fig. 2., Registers B, C, D, E, H, and L are the general-purpose registers in 8085 microprocessor. They are also called scratchpad registers.

- In almost all arithmetic and logical operations, these registers are used as the second operands, the first operand being the accumulator.

- The general purpose registers are all 8-bit registers but they can be handled as 16-bit registers as well. This can be achieved by combining the register pairs B and C, D and E, and H and L to perform 16-bit operations. They are then named register pairs BC, DE, and HL, respectively.

3. Special Purpose Registers

Accumulator:

- The accumulator is an 8-bit register. It is used to store 8-bit data and to perform arithmetic and logical operations.

- The output of an operation is also stored in the accumulator.

- The accumulator is identified as register A in the instruction set of the 8085.

- The 8085 microprocessors communicate with input/output devices only through the accumulator.

Flag Register:

- This is a special 8-bit register. Each bit of the flag register is quite independent of the others.

- In all other registers, each bit is part of a single binary byte value and hence each bit would have numerical value.

- The flag is an 8-bit register used to indicate the status of a recent arithmetic or logical operation. It may be set or reset after an arithmetic or logical operation according to the condition of the processed data.

- The 5 flag bits are zero (Z), carry (CY), sign (S), parity (P), and auxiliary carry (AC). The bit positions of the flag bits are shown in Fig. 3. The remaining 3 bits (D1, D3, and D5) of the flag register remain unassigned (they are marked as don’t cares, X).

- Any flag register bit is said to be ‘Set’ when its value is 1 and ‘Cleared’ when its value is 0.

a ) Sign Flag (S):

The sign flag is just a copy of the bit D7 (Most Significant Bit- MSB) of the accumulator. A negative number has a 1 in bit 7 and a positive number has a 0 in 2’s complement representation. This flag indicates the sign of the number. This flag can be used in signed arithmetic operations.

b) Zero Flag (Z):

The zero flag is set if an arithmetic operation results in a zero. It sets, i.e., it changes to binary 1 if the result in the accumulator is zero. If not, it remains reset, i.e., at binary 0.

c) Carry Flag (CY):

The carry flag is set when a carry is generated in the process of an arithmetic operation in the accumulator. When addition is carried out, it sometimes results in a 9th bit being carried over to the next byte. The CY flag copies the value of the carry, which is an extra bit. From D7. It also reflects the value of the borrow in subtractions.

d) Auxiliary Carry Flag (AC):

The auxiliary carry flag is set when an auxiliary carry is generated in the process of an arithmetic operation in the accumulator, i.e., when a carry results from bit D3 and passes on to D4 (from the lower nibble to the higher nibble). This carry is also called half-carry. It may also occur in the process of a subtraction operation. This flag is also set if the subtraction operation results in borrow.

e) Parity Flag (P):

The parity flag is set if the content of the accumulator after an arithmetic operation has an even number of 1s. Otherwise, the parity flag is reset. It is set for operation in the even parity mode.

Program Counter (PC):

Program Counter (PC) is a 16-bit register that always points to the address of the next instruction to be executed.

- In other words, this register is used to sequence the execution of the instructions.

- After execution of every instruction, the content of the memory location indicated by the PC is moved to the instruction register and the PC is loaded with the next address. It keeps track of a program by counting the memory address from which the next byte is to be fetched, and hence the name program counter.

Stack Pointer (SP):

- Stack is an array of memory locations organized in last-in first-out (LIFO) or First-In Last-Out (FILO) fashion.

- It is accessed using a 16-bit pointer register called stack pointer, which holds the address of the memory location of the top of the stack.

- The programmer can reverse and allocate a series of RAM locations to be used as a stack and accordingly initialize the stack pointer.

- In all microprocessor-based system, the stack is mainly used to store the return address of the main program when sub-routine is called.

- While the programmer uses the stack for storage and retrieval of data, the microprocessor uses the stack during sub-routine calls.

4. Instruction Register and Decoder

- Instruction Register and Decoder is an 8-bit register that usually temporarily stores the instructions drawn from memory locations, before their actual execution.

- The content of the register is decoded by the decoder circuitry, where the nature of the operation to be performed is decided.

- In addition, there are two temporary registers W and Z, which are controlled internally and not available for the user access.

5. Timing and Control Unit

The Timing and Control Unit (TCU) in the 8085 microprocessor is a decisive component responsible for generating and controlling the timing signals required for the execution of instructions. It manages the sequencing of various microprocessor operations and ensures that instructions are executed in the correct order and at the appropriate times. Brief descriptions of the Timing and Control Unit parameters in the 8085 microprocessor are listed below:

Clock Signals:

- The TCU generates the clock signals required to synchronize the operation of the microprocessor.

- The 8085 typically operates at a clock speed of 3 MHz, which means that it generates three million clock cycles per second.

Clock Generator:

- In some 8085 systems, the TCU may include a clock generator circuit that generates the system’s clock signal.

- This clock signal provides the timing reference for the entire microprocessor.

Machine Cycle: The TCU divides each clock cycle into a series of machine cycles, each with specific functions. The key machine cycles in the 8085 are:

- Opcode Fetch Cycle: In this cycle, the microprocessor fetches the opcode (instruction code) from memory. It involves sending the memory address from the Program Counter (PC) to the memory, reading the opcode, and incrementing the PC.

- Memory Read Cycle: This cycle is used to read data from memory into registers or other temporary storage locations. It involves sending the memory address to memory, reading the data, and storing it in the appropriate register.

- Memory Write Cycle: During this cycle, the microprocessor writes data from registers to memory. It involves sending the memory address and data to memory for storage.

- I/O Read and Write Cycles: Similar to memory read and write cycles, but used for input and output operations to and from peripheral devices.

Control Signals: The TCU generates various control signals that coordinate the microprocessor’s operations. These signals include:

- RD (Read): Activated during memory read and I/O read cycles to indicate that data is being read from memory or an input device.

- WR (Write): Activated during memory write and I/O write cycles to indicate that data is being written to memory or an output device.

- ALE (Address Latch Enable): Used to latch the lower byte of the address bus during memory and I/O operations.

- CLKOUT: An output signal that can be used to synchronize other devices with the 8085’s clock.

- RESET: Used to reset the microprocessor, clearing its state and setting the PC to a predefined address.

Instruction Sequencing:

- The TCU ensures that instructions are executed in the correct sequence by controlling the flow of control signals and machine cycles.

- It fetches the next instruction, decodes it, and initiates the required machine cycles to execute the instruction.

Interrupt Handling:

- The TCU manages interrupt requests from external devices by generating the INTA (Interrupt Acknowledge) signal and ensuring that the microprocessor correctly responds to interrupts.

S0, S1:

S0, S1, and IO/M (Input/Output Memory) are control signals used for interfacing with memory and input/output devices.

- S0 and S1 are status or control signals used for memory and I/O device interfacing.

- Together, S0 and S1 signals form a 2-bit combination that specifies the machine cycle the microprocessor is currently in.

- These signals are primarily used to distinguish between different types of memory and I/O operations.

- Depending on the state of S0 and S1 during a machine cycle, the microprocessor can access memory or interact with peripheral devices.

The following table summarizes the meaning of different S0-S1 combinations:

| S1 | S0 | Status |

|---|---|---|

| 0 | 0 | Halt |

| 0 | 1 | Write |

| 1 | 0 | Read |

| 1 | 1 | Fetch |

IO/M’ (Input/Output Memory):

- The IO/M’ signal is used in conjunction with the S0 and S1 signals to distinguish between memory and I/O operations during the machine cycle.

- When IO/M’ is low (IO/M’ = 0), it indicates that the microprocessor is performing a memory operation (either memory read or memory write).

- When IO/M’ is high (IO/M’ = 1), it indicates that the microprocessor is performing an I/O operation (either input or output).

- For example, during a memory read cycle, S0 = 0, S1 = 1, and IO/M’ = 0, indicating that the microprocessor is reading data from memory. Conversely, during an I/O operation, S0 = 1, S1 = 1, and IO/M’ = 1, indicating that the microprocessor is performing an input or output operation.

HOLD:

- The signal indicates that a peripheral such as a direct memory access (DMA) controller is requesting the use of the address and data bus.

HLDA:

- It is an acknowledgement signal that is sent in response to the Hold request.

- During the Hold state, the peripheral (I/O) devices get control over the data and address buses for data transfer to and from memory. This operation is called Direct Memory Access (DMA).

- DMA is useful when high-speed peripherals want to transfer data to and from memory. The processor does not intervene during this period.

READY:

- This signal serves to delay the microprocessor read/write signals until a slow-responding peripheral is ready to send or accept data.

- If this signal goes low, then the microprocessor is allowed to wait for an integral number of clock cycles until READY becomes high.

- The READY signal must be synchronized with the processor clock.

6. Serial I/O Control Unit

8085 microprocessor features a Serial Input/Output Control Unit that provides basic serial communication capabilities.

SOD: (Serial Output Data)

- The SOD (Serial Output Data) pin of the Intel 8085 microprocessor is an output pin used for serial data output in certain modes of operation, specifically when the microprocessor is configured for serial data transfer.

- In serial communication modes, the SOD pin is used to transmit data serially to external devices or peripherals. When data is ready to be transmitted, it is shifted out bit by bit through the SOD pin.

- To enable serial communication and use the SOD pin, appropriate control signals and programming must be set up in the microprocessor to configure it for serial data transfer.

SID: (Serial Input Data)

- The SID (Serial Input Data) pin of the Intel 8085 microprocessor is an input pin used for receiving serial data in certain modes of operation, particularly when the microprocessor is configured for serial data transfer.

- In serial communication modes, the SID pin is used to receive serial data from external devices or peripherals. Data is inputted to the microprocessor through this pin, typically in a serial format with start and stop bits that frame each byte of data.

- To use the SID pin for serial data reception, appropriate control signals and programming must be set up in the microprocessor to configure it for serial data transfer.

7. Interrupt Control Unit

The Interrupt Control Unit (ICU) is a crucial component of a microprocessor’s architecture, including the Intel 8085 microprocessor. Its primary function is to manage and control interrupt requests from external devices and internal sources, allowing the microprocessor to respond to events that require immediate attention or higher priority than the current task. Five interrupt signals, INTR, RST 5.5, RST 6.5, RST 7.5 TRAP are available to facilitate the processor to receive and acknowledge the interrupt from the peripherals.

- INTR (Interrupt Request) is a hardware interrupt request line of 8085 microprocessor. It is one of the five interrupt lines available in the 8085 architecture, each with its own priority level. INTR is the lowest-priority interrupt line among them.

- RST 5.5, RST 6.5 and RST 7.5 are the RST (Restart) instructions of 8085 microprocessor. These are a group of hardware interrupts that allow the program to jump to specific predefined memory addresses. These restart instructions provide a means for the program to call specific subroutines or interrupt service routines (ISRs) for various purposes.

- TRAP is a non-maskable interrupt. It can not be stopped or over ridden by any command. It has the highest priority among all 8085 interrupts.